[Documento Vivo, 27 de agosto de 2025 | Revisión 40]

Índice

Introducción

EL ESTANDAR PCI EXPRESS

¿Qué son PCI Express y PCI Express 6

Evolución de PCI Express: de PCIe 1.0 a PCIe 6.0 y mejoras logradas en este respecto a PCIe 5.

El Consorcio Industrial Tecnológico Global PCI-SIG

PROYECCIÓN DE PCIE HACIA 2040

Proyección estimada de PCIe en la producción y en las finanzas, de 2025 a 2040

Probables sinergías de escalación del hardware PCIe 6,7 y 8

PCI 6 es clave en la democratización de la Intelectrónica

eL IMPACTO tecnoACELERADOR DE PCIE 6

Impacto en el Metaverso, la Robotización, la Bioelectrónica y la Intelectrónica

Aceleración que trae PCI 6 a la Capa Intelectrónica Universal (CIU) actualmente en formación

La potenciación en ciernes de la Onda Cultural post PCIe 6 y Revolución Científica

NOTAS

Bibliografía

ANEXOS

Recursos intelectrónicos empleados

Glosario de anglicismos (técnicos y de uso común)

Glosario de Acrónimos

Introducción

Nos encontramos inmersos en la llamada Civilización de la Inferencia o Era de la Inteligencia Artificial, que se despliega como una Ola Tecnológica Global en rápida eclosión, caracterizada por el surgimiento de un medio ambiente intelectrónico. Se trata del desarrollo, durante nuestra actualidad histórica desde inicios de 2010 hacia los años 2050, de una Capa Intelectrónica Universal (CIU) o de Inteligencia Artificial, en toda la infraestructura urbana y el medio ambiente humano.

Esta capa intelectrónica ubicua integra y engloba a El Metaverso, al creciente y en vías de masificación Parque Robótico Mundial, a los incipientes Entornos Bioelectrónicos aún escasos y dispersos por algunas docenas de biolaboratorios avanzados en varios continentes, y al Parque Mundial de Ordenadores y de Dispositivos IoT (1) .

Los cambios en la geografía, el urbanismo y el medio ambiente humano en general, traidos por el desarrollo de la maquinica microelectrónica, la automatización de procesos y la cibernética digital, se han ido convirtiendo en un tsunami o megaola de transformación tecnológica que tiene un profundo impacto en todas las ciencias, técnicas y disciplinas, y así nos está trayendo a una Revolución Intelectual y, sin duda, también social, pero también a una Revolución Ciéntifica que se encuentra en sus prolegómenos, mientras desencadena una Onda Cultural de renovación y revolución de las relaciones humanas.

La Revolución Ciéntifica en ciernes es una Revolución Científica muy peculiar, es la Primera Revolución Científica General, dirigida por un vanguardias de trabajadores intelectuales y operativos en colaboración con un sujeto o supersujeto nuevo, el sujeto tecnológico que llamamos la IA.

En efecto, las poderosas Inteligencias Artificiales Generativa, Agéntica y General, que son un resultado de este cambio tecológico histórico, conducen al auge y la aceleración de la biotecnología, la nanotecnología, la astronomía, la física, las matemáticas, la ciencia de materiales, la medicina, la robótica… la naútica, la astronáutica, el marketing, las artes, la espiritualidad, la cibernética política y social… llevándonos a un especialmente enérgico impulso al desarrollo de las fuerzas productivas que es el más acelerado de la historia, hasta la fecha.

La tranformación tecnológica globlal produce un aparato cognitivo mundial que genera, capta y consume volúmenes de datos sin precedentes — se proyecta que más de 40 mil millones de dispositivos IoT producirán unos 80 zettabytes (2) de datos ya en este 2025 — y gran parte de esa información deberá procesarse en tiempo real fuera de los centros de datos tradicionales, directamente en dispositivos y redes de borde. Y, de hecho, sin un aumento muy significativo de la capacidad de computo instalada in situ en las vías, redes, nódulos, residencias, talleres, articulaciones y geografías de la totalidad social no puede construirse El Metaverso.

En este contexto, se requieren interconexiones de altísimo rendimiento que permitan mover y analizar datos masivos con latencias (3) ínfimas, dentro y fuera de las casas, y, a la vez, una distribución ubicua también de inteligencia artificial en el medio ambiente humano, por medio de la instalación de la Capa Intelectrónica Universal.

Pues bien, en el corazón de esta revolución del ecosistema en general, y de la inferencia intelectrónica en particular, se encuentra PCI Express y, específicamente en esta decenio venidero, PCI Express 6.0; el estandar y la nueva generación del estandar de bus de interconexión de periféricos.

EL ESTANDAR PCI EXPRESS

Siguiendo la estela del artículo sobre la Civilización de la Inferencia en este mismo web (Ver) oteamos ahora un impulso adicional a la megaola de tecnoaceleración comenzando a formarse a partir del impulso catalizador del estandar industrial PCIe 6, en primer lugar, y, pronto, de PCIe 7 y 8.

Si queremos apreciar el impacto que pueden tener los grandes cambios en el software, basta con que recordemos que se está diciendo que el cese de las actualizaciones de Windows XP dejará un millón y medio de toneladas de componentes electrónicos y de hardware informáticos obsoletos, y 240 millones de ordenadores fuera de servicio (5), pero ¿y lo contrario? ¿qué ocurre cuando son los estandares de hardware los que se renuevan de manera rítmica y progresiva, impactando creciente y masivamente en todo el aparato cognitivo y digital mundial?

Recordemos que Internet realizó su histórico despegue mundial hacia la universalización a partir del surgimiento de dos estándares, HTTP (Protocolo de Transferencia de HiperTexto) y HTML (Lenguaje de Marcado de HiperTexto), que generaban una infraestructura digital y telemática renovadora a dimensiones históricas, a partir del desarrollo de la microelectrónica y los semiconductores. La llamábamos La Web, o la Red de Amplitud Mundial, RAM, o, en inglés, World Wide Web, y está coordinada por el organismo de estandarización Worlwide Wide Web Consortium, W3 (4). Conviene, pues, no menospreciar el poder transformador de un esfuerzo socio-industrial de estandarización tecnológica avanzada.

¿Qué son PCI Express y PCIe 6?

PCI (Peripheral Component Interconnect / Interconexión de Componentes Periféricos) fue el bus paralelo introducido por la empresa Intel en 1992 para conectar tarjetas de expansión a la placa base (4). Con el tiempo quedó limitado en ancho de banda y compartía todas las señales en un único canal.

PCI Express (PCIe) nació en 2003 como evolución, serie y punto-a-punto de PCI. Cada dispositivo cuenta con uno o varios carriles dedicados (lanes) que combinan transmisión y recepción full-dúplex, eliminando los cuellos de botella del bus paralelo. La arquitectura PCIe permite escalar ancho de banda añadiendo más carriles (x1, x4, x8, x16) o aumentando la velocidad de señal cada generación del estandar.

PCIe 6.0 es la sexta generación del estándar PCIe (ratificada en enero de 2022 por el consorcio PCI-SIG [5]). Este nuevo estandar de conexión de dispositivos periféricos expande las capacidades de flujo datos en el interior de los ordenadores y entre ordenadores, por lo que mejora la telemática, los resultados de las redes y la potencia informática e inferencial en general de la infraestructura computacional.

En cada generación de estandar PCIe expande las capacidades de la infraestructura, los ordenadores y los dispositivos, dentro de una política expansiva consciente y negociada en la industria y, seguramente, en los niveles políticos decisorios de los principales Estados del mundo, si es que pueden impedir la tendencia al desarrollo del sujeto automático capitalista [Robert Kurz] aún en funciones. Y es que el motor acelerador es todavía el sistema capitalista y el mercado mundial, entre la Teoría del Derrumbe y un Ciclo Largo de Acumulación Kondratieff 6, hacia un colaso previsible en un límite absoluto de la acumulación en torno a los años 2055-60.

No solo las poblaciones exigen mejoras básicas de sus estandares de vida en todo el mundo, y es retroaccionario negarselas, también las empresas piden mayores capacidades, los paises necesitan mejores infraestructuras, las empresas fabricantes y consumidoras de hardware buscan ampliar sus catalogos y mejorar sus productos, y los trabajadores buscan retos productivos en la lucha por la producción, en la carrera de la competencia y la colaboración, que también es un reto, y, finalmente, este capitalismo industrial informático, tecnológico, impone los estandares que necesitan el mercado y los principales monopolios sectoriales o territoriales y empresas para asegurar su expansión.

Las fuerzas productivas impulsan este sistema pero también surgen sujetos históricos que impulsan o intentan impulsar con diversas justificaciones contenciones cuando no detenciones del desarrollo de la producción, y, en este caso, de su producción cualitativa estratégicamente ahora más alta y productiva, la inferencia artificial, la IA.

Por tanto, en términos socio-económicos PCIe es una convergencia del capital productivo en el plano de la colaboración y la competencia para dar viabilidad a su existencia y a la del aparato productivo mundial. Y PCIe 6 es un impulso concreto a la expansión motorizado por el capital industrial productor de hardware. El recorrido de esta expansión del capital industrial de hardware es bien conocido:

Evolución de PCI Express: de PCIe 1.0 a PCIe 6.0 y mejoras logradas e este respecto a PCIe 5.

Desde su introducción en 2003, la arquitectura PCI Express se ha consolidado como la interfaz dominante en la informática, aumentando exponencialmente el rendimiento, con cada generación y manteniendo compatibilidad hacia atrás. El consorcio PCI-SIG publicó la especificación final de PCIe 6.0 a comienzos de 2022, cumpliendo con su hoja de ruta acelerada.

| Generación (año) | Tasa de datos (GT/s) | Ancho de banda x16 (GB/s) |

|---|---|---|

| PCIe 1.0 (2003) | 2.5 GT/s | ~4 GB/s |

| PCIe 2.0 (2007) | 5 GT/s | ~8 GB/s |

| PCIe 3.0 (2010) | 8 GT/s | ~16 GB/s |

| PCIe 4.0 (2017) | 16 GT/s | ~32 GB/s |

| PCIe 5.0 (2019) | 32 GT/s | ~64 GB/s |

| PCIe 6.0 (2022) | 64 GT/s | ~128 GB/s |

PCIe 6.0 introduce una nueva técnica de modulación llamada PAM4 (Pulse Amplitude Modulation, 4 niveles), que permite enviar el doble de información en el mismo intervalo de tiempo respecto a la anterior modulación NRZ. Además, incorpora mecanismos de corrección de errores FEC (Forward Error Correction) para mantener la integridad de los datos con latencias extremadamente bajas.

La introducción de paquetes FLIT (Flow Control Units) de tamaño fijo mejora aún más la eficiencia del protocolo, optimizando el ancho de banda y reduciendo los errores en transmisiones de datos.

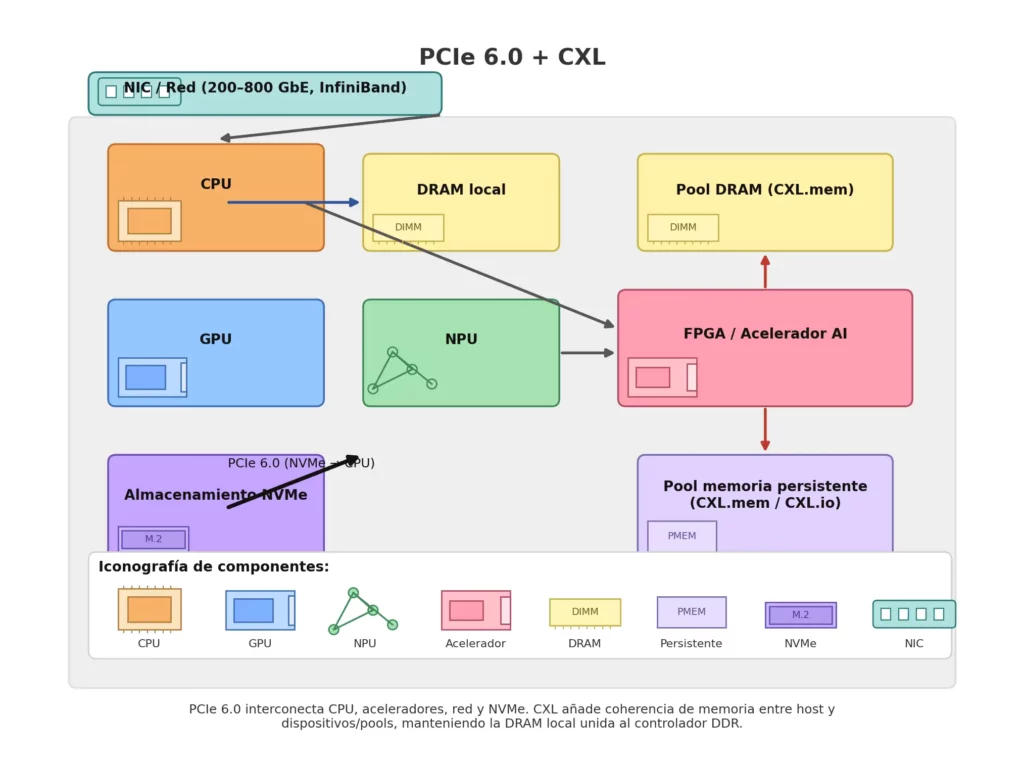

Una de las sinergias más relevantes es su integración con el estándar Compute Express Link (CXL), que se apoya en la infraestructura física de PCIe 6.0 para ofrecer coherencia de memoria entre CPU, GPU, aceleradores y almacenamiento persistente. Esto habilita arquitecturas de computación heterogénea donde diferentes procesadores comparten datos en tiempo real sin copias redundantes, lo que reduce la latencia y maximiza la utilización de recursos. En centros de datos, la combinación PCIe 6.0 + CXL abre la puerta a pools de memoria desagregada y escalable, permitiendo que la memoria y los aceleradores se asignen dinámicamente según la carga de trabajo, un avance crítico para la IA, la analítica masiva y El Metaverso.

Mejoras Técnicas en PCIe 6.0 vs PCIe 5.0

| Característica | PCIe 5.0 | PCIe 6.0 |

|---|---|---|

| Velocidad de datos | 32 GT/s | 64 GT/s |

| Modulación | NRZ | PAM4 |

| Corrección de Errores (FEC) | No requerida | Incluida |

| Formato de paquetes | Variable | FLIT (fijos) |

| Eficiencia Energética | Alta | Muy Alta (Estado L0p) |

| Ancho de banda bidireccional (x16)* | 128 GB/s | 256 GB/s |

| Latencia | Baja | Muy Baja (mejoras en FEC) |

| Compatibilidad retroactiva | Sí | Sí |

*Ancho de banda unidireccional en configuración x16 (PCIe es full dúplex, el enlace x16 alcanza el doble de GB/s en comunicación bidireccional).

Así pues, PCIe 6.0 duplicó el ancho de banda respecto a su predecesor PCI 5, e introdujo mejoras tecnológicas muy significativas para satisfacer las demandas de la Era de la IA y la computación inmersiva, pero solo en el mercado industrial, retrasándose significamente, sea por dificultades técnicas, mercantiles o políticas, en su difusión hacia el mercado de consumo particular y de la pequeña empresa.

El Consorcio Industrial Tecnológico Global PCI-SIG

La organización de las innovaciones y reevaluaciones del estandar PCIe, con tan gran número de intereses abarcados, pues puede dejar obsoleto a enormes porciones del parque computacional mundial o retrasar los avances en capacidades de amplios segmentos del mercado mundial de computación, no es fácil.

La centralización política del estandar la realiza PCI-SIG (Peripheral Component Interconnect Special Interest Group / Grupo de Interés Especial de la Interconexión de Componentes Periféricos) que es un consorcio industrial sin ánimo de lucro fundado en 1992 y convertido formalmente en nonprofit en 2000, con sede en Beaverton, Oregón, EE.UU. Su misión es definir, mantener y certificar los estándares PCI, PCI-X y especialmente PCI Express (PCIe), que constituyen la columna vertebral del I/O de alta velocidad en PCs, servidores, centros de datos y sistemas embebidos.

PCI-SIG está integrado por más de 1 000 empresas miembro a nivel global, desde grandes fabricantes de semiconductores hasta proveedores de IP, test, OEMs y centros de datos. Entre las empresas más destacadas se encuentran: AMD, Intel, IBM, NVIDIA, Qualcomm, ARM, Dell EMC y Synopsys, que representan sectores como chips, gráficas, centros de datos, redes y diseño electrónico.

El consorcio no solo publica especificaciones —como PCIe 6.0 (lanzada en 2022) y PCIe 7.0 (Lanzada en 2025)— sino que también gestiona el programa de conformidad, certificando interoperabilidad y retrocompatibilidad mediante talleres de pruebas (Compliance Workshops) y el listado de integradores (Integrators List). También organiza conferencias (Developers Conference | Conferencia de Desarrolladores) y mantiene un modelo RAND (Reasonable and Non-Discriminatory | Razonable y No discriminatorio) para licencias, lo que le permite preservar una adopción eficiente y escalable del estándar.

Además de PCIe, existen otros métodos de conectividad periférica no estándar —como USB-C ampliado, enlaces ópticos propietarios, o redes de interconexión fuera del ecosistema PCI—, aunque estos carecen de la compatibilidad y robustez certificadas por PCI-SIG. A futuro, el consorcio trabaja en colaboración con tecnologías emergentes como CXL, crucial como soporte de infraestructura de la capa de inferencia, UCIe y, hacia la fotónica, enlaces ópticos estandarizados, apuntando a una arquitectura heterogénea y coherente entre aceleradores, memoria y CPUs. Si bien existen debates internos sobre el ritmo de adopción o complejidad del estándar, el modelo colaborativo y la adaptación tecnológica continua han mantenido al ecosistema fuerte y coordinado.

Principales Empresas Miembro y sus Sectores

| Sector | Empresas más representativas |

|---|---|

| Semiconductores / Chips | AMD, Intel, Qualcomm, ARM, Synopsys |

| Gráficas / Aceleradores | NVIDIA |

| Computación / Servidores | IBM, Dell EMC |

| Redes / Interconexión | Cisco, Marvell, Mellanox (NVIDIA) |

| Cables y Conectores | CopperLink, Molex, Amphenol |

| Test y Certificación | Keysight, Teledyne LeCroy, GRL (Authorized Test Lab) |

| IP / Diseño | Synopsys, Xilinx, Cadence |

| Almacenamiento / SSD | Kioxia, Western Digital, ADATA |

| Fabricación / OEMs | Foxconn, Acer, Advantech |

| Estándares Relacionados / Consorcios | PICMG, USB-IF |

eL IMPACTO tecnoACELERADOR DE PCIE 6

Impacto estimado de PCIe en la producción y en las finanzas, de 2025 a 2040

El estándar PCI Express (PCIe) es, como estamos viendo, la columna vertebral de gran parte del hardware moderno: tarjetas gráficas, unidades SSD NVMe, placas base, servidores y tarjetas de red. Aunque su impacto económico directo en 2025 se estima en unos 190 mil millones de dólares anuales (~0,18 % del PIB mundial), su importancia real se amplifica enormemente cuando se consideran los sectores que dependen de él de forma indirecta.

La computación en la nube, las plataformas de redes sociales, el sector de videojuegos, la producción cinematográfica y la gestión digital de pequeñas y medianas empresas dependen de infraestructura que utiliza PCIe. En 2025, estos sectores representan un valor agregado combinado de entre 1,1 y 1,3 billones de dólares anuales, equivalente a más del 1 % del PIB mundial. Sin PCIe, gran parte de esta infraestructura no podría funcionar con la eficiencia y velocidad actuales.

Las inversiones actuales en hardware son masivas. Grandes plataformas tecnológicas de redes sociales como Meta, Google, Microsoft, Amazon, y Open.ai, (aunque esta última todavía no es una plataforma tecnologica de red social de inferencia), están destinando decenas de miles de millones de dólares cada una a ampliar centros de datos e integrar hardware para IA en gran parte del mundo. En conjunto, se estima un gasto global de hasta 3 billones de dólares en la próxima década solo en infraestructura de IA y centros de datos, gran parte de ella construida sobre hardware PCIe.

Mirando hacia el futuro, la proyección para 2040 indica un crecimiento sostenido. El mercado global de computación en la nube, que podría alcanzar 912 mil millones USD en 2025, superaría los 7,4 billones USD en 2040. La infraestructura de IA y data centers pasaría de unos 300 mil millones USD a más de 1,25 billones USD, mientras que los videojuegos crecerían hasta rondar los 350 mil millones USD, sino más a impulso de las diversas facetas de El Metaverso.

En términos agregados, los sectores habilitados por infraestructura PCIe podrían mover alrededor de 9 billones USD anuales en 2040, lo que representaría un estimado aprox. de entre el 5 y el 9 % del PIB mundial proyectado, dependiendo de las proporciones del crecimiento de otros sectores y del crecimiento del PIB mundial. Esto consolidaría a PCIe como un pilar silencioso, pero fundamental, de la economía digital global.

| Concepto | 2025 (USD) | 2040 (USD) |

|---|---|---|

| Computación en la nube | 912 mil millones | ~7,4 billones |

| IA / Data Centers | 300 mil millones | ~1,25 billones |

| Videojuegos | 189 mil millones | ~350 mil millones |

| Total estimado | ~1,4 billones | ~9 billones |

Nota: Cifras aproximadas basadas en datos de 2023-2025 de Grand View Research, Newzoo, Precedence Research, Financial Times y estimaciones propias sobre proyecciones de crecimiento a 2040.(9)

Probables sinergías de escalación del hardware PCIe 6 a 8

Pero más acá de las perspectivas de crecimiento del volumen de negocio, esta la cuestión del escalado del hardware propulsado por PCIe 6, que es estratégica para la ubicación de los sujetos, desde las clases, las empresas, las organizaciones e instituciones, o las familias y los sujetos de todo tipo, desde autores a consumidores.

La Hoja de Ruta y su cronograma estimado de PCIExpress desde 2022 a 2040 sería más o menos esta:

| Año | Hito PCIe 6.0 | Difusión estimada | Hito PCIe 7.0 | Difusión estimada | Hito PCIe 8.0 | Difusión estimada |

|---|---|---|---|---|---|---|

| 2022 | Especificación 1.0 final; inicio IP/PHY en laboratorios | Validación de silicio y pruebas SI | — | — | — | — |

| 2024 | Demostraciones públicas (FMS, DesignCon); retimers y switches prototipo | Equipos de test; Early-Access cards | Borrador 0.7 publicado; cierre de comentarios | Revisión de miembros | Objetivos técnicos planteados; estudios de viabilidad SerDes | Laboratorio (pre-IP) |

| 2025 | Lista de Integradores PCIe 6; primeros servidores IA (Q4) | Hiperescala/HPC inicial | Especificación 1.0 (junio); kits de conformidad iniciales | Path-finding óptico y cables activos | Anuncio de trabajo formal; borrador temprano (0.x) | IP/PHY temprana; partners piloto |

| 2026 – 2027 | Workstations pro y edge servers; ecosistema CXL 3.x sobre Gen6 | Empresa y telecom | Primeros test-chips Gen7; validaciones de placa/backplane | Alpha silicon | Borrador 0.7–0.9; primeras demostraciones de canal a 256 GT/s | Laboratorio avanzado |

| 2028 – 2029 | Placas base entusiastas; SSD Gen6; NIC 800 GbE | Consumo avanzado / prosumer | Plataformas HPC piloto; switches/cabling activos Gen7 | Centros de datos selectos | Especificación 1.0 (≈2028); test-chips Gen8 (2029) | Pilotos DC/HPC muy selectivos |

| 2030 – 2031 | Masificación en PC de gama media; CXL desplegado en enterprise | Mainstream | Servidores generalistas Gen7; SSD/NIC Gen7 | Despliegue amplio 2030–2031 | Primeras plataformas HPC/IA Gen8; retimers de 2.ª gen | Hiperescala inicial |

| 2032 – 2033 | Consolidación en consumo; coste/GB NVMe Gen6 a la baja | Consumo y pyme | Desktop entusiasta/prosumer; ecosistema maduro | Masivo en enterprise/DC | Adopción temprana en DC premium; switches Gen8 piloto | Centros de datos punteros |

| 2034 – 2035 | — | — | Dominante en DC; redes internas 1.6 TbE; CXL sobre Gen7 | Estándar de referencia | Entrada en enterprise; placas WS/creator alto nivel | Despliegue inicial enterprise/WS |

| 2036 – 2037 | — | — | — | — | Servidores generalistas Gen8; SSD/NIC Gen8 | Adopción amplia en DC/edge |

| 2038 – 2040 | — | — | — | — | Prosumer/entusiasta alto; exploración óptica integrada | Consumo avanzado y enterprise mainstream |

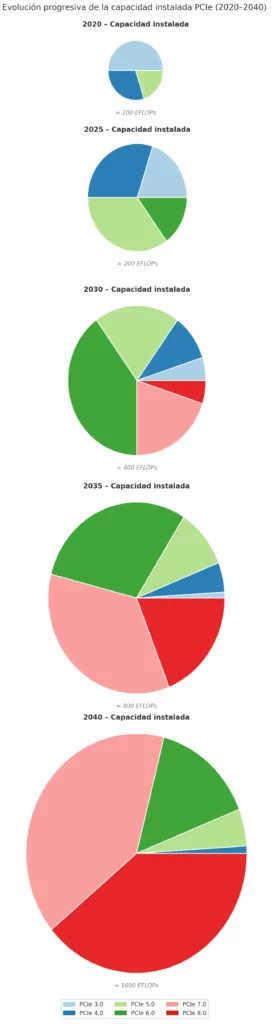

Entre 2025 y 2030, PCIe 6.0 marcará el inicio de una etapa centrada en IA y memoria compartida: PAM4 + FEC y el soporte nativo de CXL 3.x permiten “pools” de memoria coherente entre CPU, GPU y aceleradores.

Los primeros despliegues significativos de esta mezcla tecnológica van llegando como servidores AI/HPC y cloud, mientras el consumo entusiasta comenzará a ver placas compatibles a partir de 2027-2028 junto a memorias SSD Gen6 cercanos a 30 GB/s y NIC de 800 GbE de transmisión de datos.

Este salto no es meramente de ancho de banda: habilita nuevas topologías de centros de datos con switching CXL, reducción de copias y latencia, y mayor utilización de recursos, con efectos de productividad en entrenamiento e inferencia.

Las hojas de ruta de mejora, expansión y escalado de CPU y SoC refuerzan este patrón.

Entre 2025-2027, Intel (Arrow/Panther Lake), AMD (Zen 5/6), NVIDIA (Grace Next) y Apple/Qualcomm en ARM integran nodos avanzados (N3→N2/18A) y empaquetado 3D (Foveros, chiplets, on-package DRAM), alineando controladoras PCIe 6 en servidores y, de forma gradual, en estaciones de trabajo. RISC-V irrumpe en el edge de alto rendimiento, también sobre PCIe 6, con diseños orientados a computación cercana al dato. En este periodo, la relación PCIe-CXL se vuelve estratégica: PCIe aporta el transporte físico, CXL la coherencia y la semántica de memoria.

Hacia 2029-2032, la transición a PCIe 7.0 en hyperscalers y supercomputación apunta a duplicar el rendimiento efectivo por carril (hasta 128 GT/s), presionando los límites del cobre y multiplicando el uso de retimers y trazados de muy alta calidad. En este horizonte, los datos del cronograma sitúan la adopción de PCIe 7 en servidores punteros desde 2029, con presencia en equipos entusiastas a partir de 2032-2033. El incentivo económico es claro: clusters más densos, redes internas 1.6 TbE, throughput sostenido para bases de datos in-memory y sistemas de IA generativa de gran escala.

Para 2035, los escenarios plausibles muestran a PCIe 6 como estándar de consumo generalizado, mientras PCIe 7 alcanza en torno a un tercio del parque de centros de datos de vanguardia, impulsado por cargas de IA, analytics y streaming. En PC, la mezcla esperada queda repartida entre PCIe 4/5/6, con Gen6 consolidándose por la madurez de chipsets, disponibilidad de SSD rápidos y tarjetas gráficas compatibles. En servidores, la combinación 5/6/7 se decanta hacia 6-7 conforme se renuevan nodos y se estandarizan backplanes y OCP con enlaces de mayor velocidad.

Entre 2036 y 2040, el foco se traslada a PCIe 8.0 (objetivo 256 GT/s), donde se intensifica la exploración de interconexión óptica y de nuevos conectores/cables de alta integridad para distancias de chasis y rack. Si bien la adopción masiva depende de costos, consumo y madurez de ecosistemas (incluyendo compatibilidad con CXL de próxima generación), las proyecciones sitúan a PCIe 7 como dominante en Centros de Datos premium y a PCIe 6 ampliamente extendido en enterprise y consumo. PCIe 8 emergerá primero en nichos de exa/zetta-escala y sistemas con empaquetado 3D extremo, donde el coste por gigabyte/segundo justifique la transición.

Estas trayectorias están condicionadas por tres variables:

(1) la cadencia de los procesos de fabricación (High-NA EUV, N2/N1.x, 18A/14A),

(2) la evolución del coste energético y térmico por bit movido (que puede inclinar el diseño hacia óptica o nuevas geometrías de canal),

y (3) la economía del software: cuanto más rentable sea escalar modelos de IA, bases de datos y streaming sobre arquitecturas disgregadas, mayor presión habrá para adoptar generaciones superiores de PCIe. Aun con incertidumbres, el vector central es claro: PCIe 6→7→8 no solo duplica ancho de banda, sino que reconfigura la manera de componer memoria, aceleración y almacenamiento.

PCI 6 es clave en la democratización de la intelectrónica

Recordemos que Jano era el dios de la República romana. Su busto bifronte y bifaz se ponía ante las viviendas de las familias de la ResPublica romana. Una cara del dios miraba al interior de las casas, y simbolizaba la apertura de la casa a lo colectivo y su transpoarencia a la mirada pública, por ejemplo en la afirmación de no tener armnas fuera de control de la ResPública. Otra cara del dios miraba hacia afuera, hacia lo colectivo, lo público, afirmando participación de lo particular en lo colectivo. Era pues un contrato de conciencia política. Para nuestros contencionistas malthusianos pardece que no ha de existir este contrato de conciencia sino solo contencionismos de las casas particulares e incontinencia de las mediaciones de interfaz REPRESENTATIVOS DE UNA IDEOLOGÍA MUY CONCRETA, finalmente aristocracista, malthusiana, liberal, conductista, socialdemocrata y darwinista social.

El sentido común anti autogestionario, y fuera de los contratos de conciencia políticos en Res Pública colectivoparticular, nos llama a impedir la descentralización de la producción de la inferencia y podría converger en justificar en detener la difusión de las capacidades de PCI6 al gran público mundial. La difusión de sus ideas, que es cierto que en parte son reales en cuanto a las dificultades de reducir los precios de los equipos PC con hardware PCIe, de manera que se mnasifique, podrían afectar a los plazos de difusión popular de esta tecnología, y esto hay que avisarlo a quienes muy alegremente suponen estar haciendo empoderándose ante los grandes consorcios y monopolios cuando están desemperando la autogestión popular de la inferencia:

Alerto de que lo que dice este audio, que parece una versión oficial repleta de veracidad, es una verdad a medias; el mercado de consumo es también un mercado de pequeños productores, una constelación viva de producciones y creatividad que, sin al menos una parte de infraestructura propia, quedaría orillada como fuerza productiva no desarrollada. Y quizá sea la mayor fuerza productiva existente, por lo que concluir que no hace falta para una pequeña empresa o una familia o un autor o productor independiente, desarrollos de potencia computacional como los que trae PCIe 6 es erróneo.

Al contrario de lo que afirma la perspectiva del audio, la expansión y escalado de potencia, capacidades y funcionalidades de PCIe 6 en el parque de ordenadores mundial podría, sin embargo, y precisamente en base a ese mismo discurso, no ser democratizada en un área crucial: La intelectrónica popular o de la sociedad civil comunitaria. Esta afirmación está justificada en las observaciones de maniobras políticas contencionistas que buscan evitar, en nombre de la preservación del ORDEN, la expansión, crecimiento y difusión de la intelectrónica autogestionada.

A primera vista, es legitimo y hasta necesario, vista la potencia transformadora y disruptiva de la inferencia artificial en marcos sociales, políticos y culturales actuales, a veces contradictorios cuando no antagonistas. No obstante se podría estar empleando ese contencionismo legítimo para instaurar una ORDENACIÓN no consensuada ni democrática, aristocracista, en lugar de una preservación del Orden o de los órdenes concretos que evitan el caos social en la actualidad, aunque a veces, lamentablemente, tambien lo impongan.

En esta situación, no está demás apoyar la difusión de PCIe 6 hacia el uso doméstico autogestionado, mientras se sigue exigiendo que la Ordenación de la Civilización Inferencial, o de la Era de la IA, sea democrática, y respetuosa con el individuo, la autonomia de las familias, la capacidad de autogestión y la iniciativa productiva de las pequeñas empresas colaborativas.

Veremos ahora, en el siguiente apartado, por qué esta aproximación, sin monopolismos corporativos, contencionismos aristocracistas ni tecnoexclusivismos, es fundamental y abre las puertas a mejores riquezas y soluciones, con, por supuesto, el esfuerzo de todos.

La conclusión es que acelerar la capacidad productiva de la IA, de la necesidad de desplegar nodos, segmentos y redes de la capa intelectrónica en cada punto en que mejore la productividad, el gobierno de las cosas y los datos, la salud de las personas, el orden de convivencia y la relación del medio ambiente humano con el resto del medio ambiente natural, por medio de la concientización pública es el principal objetivo productivo y de servicio del conjunto del aparato productivo y la vanguardia de sus trabajadores en esta época.

Mas, ¿cuál es el rol de PCIe 6, y el resto de PCIe en el impulso a estos objetivos?

eL IMPACTO CUALITITATIVO tecnoacelerador DE PCIE 6

PCIe 6.0 es clave para mejorar, ampliar y acelerar aplicaciones que requieren transferencia masiva y en tiempo real de datos, como entornos virtuales inmersivos (El Metaverso y XR), sistemas robóticos autónomos en vehículos y manufactura, dispositivos médicos avanzados y neurotecnologías (Bioelectrónica), y para la integración ubicua de inteligencia artificial en dispositivos, incluidos robóticos, cotidianos (Intelectrónica). La velocidad y baja latencia de PCIe 6 permite un desempeño sin precedentes en estas áreas, e impulsar un progreso significativo en eficiencia, precisión y experiencia del usuario.

Es decir, PCIe 6 por si solo dobla las capacidades de crear mundos inmersivos, simulaciones recreativas o prácticas, de dotar de intelectronica interna a los robots y cobots industriales, de doblar las capacidades de las redes de servicios y domésticos, y los sistemas logísticos. El impacto en el volumen y capacidad de servicios de los centros de datos de PCIe 7, combinado con este desarrollo de borde de PCIe 6 + Inferencia será también enorme, y redoblará las capacidades de PCIe 6, y del sistema de computación social, sin olvidar las optimizaciones de energía que trae.

Mas, como vemos, su mayor importancia radica en que no es una innovación aislada: PCIe 6 es el “sistema circulatorio” de datos entre CPU, GPU, aceleradores, memorias y dispositivos de entrada/salida. Su mejora directa amplifica el rendimiento de todas las tecnologías que dependen de mover y procesar grandes volúmenes de datos en tiempo real. Y esto impacta en varias áreas clave de la Civilización de la Inferencia.

EL METAVERSO: Experiencias inmersivas y renderizado en tiempo real

El Metaverso demanda entornos virtuales fotorrealistas con latencias mínimas para evitar mareos y mantener la sensación de presencia, si lo consideramos en su sentido amplio de Realidad Extendida, Virtual 3D y Mixta, requiere una potencia de computación y maneja de flujos de datos muchísimo mayor que la que puede proveer el estandar PCI5.

PCIe 6.0 permite que GPUs de nueva generación y sistemas de renderizado distribuido compartan grandes volúmenes de texturas, modelos 3D y datos de simulación sin cuellos de botella, y prepara probables desarrollos de sistemas holográficos, intensivos en procesado y flujos de datos. Por supuesto, en experiencias colaborativas masivas, los servidores gráficos y las estaciones de trabajo podrán intercambiar datos entre sí y con dispositivos de realidad extendida (XR) con suficiente velocidad para sostener mundos virtuales complejos y persistentes, sin olvidar su producción y su almacenado local. Por mencionar solo algunos de los desarrollos potenciados por PCIe 6 en El Metaverso, citaremos a:

- Economías creadoras XR: artistas y desarrolladores pueden producir gemelos digitales y experiencias inmersivas desde equipos convencionales, sin dependencia de granjas de rendering externas.

- Telepresencia háptica: médicos operan robots quirúrgicos, – y cualquier trabajo de precisión ultracomplejo -, a cientos de kilómetros con retorno sensorial en tiempo real, habilitando cirugía remota segura.

- Aprendizaje inmersivo: laboratorios de física, química o historia recreados en entornos 3D que corren fluidos en portátiles PCIe 6, democratizando la educación práctica.

- Industria 5.0: colaboración hombre-máquina donde cobots adaptan su comportamiento al instante según datos de IA, reduciendo fatiga y accidentes.

Y hay más, mucho más que iremos viendo, Dios mediante, durante los próximos años en cuanto al desarrollo de El Metaverso potenciado por PCIe 6 y la IA.

BIOELECTRÓNICA: Procesamiento biomédico de alta resolución y wetware avanzado

En bioelectrónica, desde implantes inteligentes hasta sistemas de diagnóstico avanzado, los flujos de datos de alta resolución —electroencefalografía multicanal, imágenes médicas 8K o sensores biométricos en tiempo real— requieren mover gigabytes por segundo con latencia mínima. PCIe 6.0 posibilita que estos dispositivos transmitan datos directamente a procesadores o aceleradores de IA para un análisis inmediato, reduciendo drásticamente el tiempo entre la medición y la respuesta médica o terapéutica, y habilitando sistemas predictivos y reactivos más precisos.

En su vertiente más avanzada, que incluye el wetware (interfaces entre tejido biológico y circuitos), centros de datos con biochips y desarrollos como Neuralink, PCIe 6.0 ofrece el ancho de banda y la baja latencia para integrar flujos neuronales o biométricos en tiempo real en entornos de cómputo masivo. Esto permite que implantes, prótesis y sensores de alta precisión trabajen junto a GPUs y NPUs, sosteniendo modelos de IA capaces de decodificar señales cerebrales, detectar patrones biológicos y ejecutar acciones físicas o virtuales casi al instante.

IA: Aceleración de la capa Intelectrónica

La Intelectrónica —integración ubicua de inteligencia artificial en dispositivos y sistemas— se apoya cada vez más en arquitecturas heterogéneas, donde CPU, GPU, NPU y memorias de alto rendimiento trabajan como un conjunto integrado. PCIe 6.0 habilita y potencia este paradigma al proporcionar el ancho de banda necesario para que los distintos elementos del sistema intercambien datos masivos sin interrupciones.

Desde portátiles de diseño avanzado hasta centros de datos de IA, este estándar permite que el “silicio inteligente” se distribuya de forma más eficiente, reduciendo los cuellos de botella y potenciando la disponibilidad de datos, información e inferencia para la toma de decisiones en tiempo real en cualquier punto de la Civilización Inferencial.

Las profundizaciones y sinergias entre las nuevas infraestructuras, equipos y redes fundados en bioelectrónica, intelectrónica, metaversalidad y robótica, profundizadas y potenciadas con PCIe 6, que dobla en capacidad y acelera en velocidad su potencia informacional, van, por tanto, a ser claves en la propulsión de la Onda Cultural, ya en enérgica formación, que instaura la Civilización de la Inferencia.

Merece especial atención el campo y sector estratégico, productor de medios de producción, actualmente en acelerado desarrollo y con una colosal concentración de inversiones, de la Intelectrónica, o Inteligencia Artificial, cuya búsqueda del «Santo Grial» de la ASI [Superinteligencia Artificial] y carrera por generar las AGIs [Inteligencias Artificiales Generales] (6) y las mayores y mejores AGIs posibles copan las principales debates teóricos y filosóficos de la actualidad.

La carrera por el primer puesto en la lucha por la producción intelectrónica a todo nivel y escala, la luchas políticas por evitar o lograr impactos positivos, capturar valor y riquezas, o transformar en poderes particulares los resultados de esta gran ola de tecnotransformación global se centran ahora especialmente, en torbellino, en torno a la IA, pero, a la vez, es de algún modo un avance de la civilización con todos sus riesgos y posibilidades positivas que concierne a todos.

En este panorama hay, no obstante, una parte política pro gubernamentista global, insisto, de ideología malthusiana, que prefiere contener la megaola hasta estar segura de lograr sus objetivos de poder y control hipercentralizador y concentrador toticonductista anti descentralización autogestionaria segura, aunque de la seguridad democrática y no de la seguridad dominante hoy aristocracista.

Algunos llegan hasta el extremismo de pretender detener mediante regulaciones asfixiantes y disuasorias de la Innovación y la autogestión democrática de la tecnología a todo este desarrollo de la capa intelectrónica. Evidentemente, a estos sujetos políticos no puede gustarles mucho la sub-ola PCIe 6 catalizadora de la aceleración de la expansión de la, estratégica en todos los sentidos, capa intelectrónica.

La Intelectrónica, en efecto, describe la integración profunda de Inteligencia Artificial en cada nivel de la electrónica moderna: desde sensores del IoT y electrodomésticos hasta servidores de hiperescala. Esta nueva capa computacional requiere mover modelos de datos masivos y parámetros de red neuronal con la menor latencia posible.

PCIe 6.0 duplica el caudal de su predecesor PCIe 5 (hasta 256 GB/s bidireccionales en x16), convirtiéndose en la autopista interna para:

- Entrenamiento distribuido de modelos LLM y visión: la mayor velocidad reduce el tiempo de sincronización de gradientes entre GPUs, acelerando ciclos de entrenamiento (7).

- Inferencia en tiempo real: servidores con múltiples aceleradores IA (GPU, TPU, FPGA, ASIC) intercambian lotes de datos sin cuellos de botella.

- Edge Computing: gateways industriales y vehículos autónomos procesan localmente streams de cámara 8K o LiDAR con latencia <10 ms gracias a backplanes PCIe 6.0.

- CXL 3.0 sobre PCIe 6.0: permite a CPU y aceleradores compartir un mismo pool de memoria coherente, eliminando copias y reduciendo consumo energético.

Fabricantes como NVIDIA, AMD, Intel y Broadcom ya muestran prototipos de switches y tarjetas IA con controladoras PCIe 6.0, apuntando a despliegues comerciales en centros de datos entre 2025-2026. Conforme la generación 5.0 se consolide en el mercado de consumo, la 6.0 habilitará nuevas arquitecturas heterogéneas donde el silicio inteligente sea tan ubicuo como la propia memoria DRAM (8).

Estos avances en capacidades impactan, a su vez, percutiendo unas mejores y mayores capacidades en la Robótica, lo que abarata muchos medios de desarrollo que refuerzan el proceso. Las sinergias de mejora y aceleración interactiva se multiplican..,

Robótica: Respuesta más rápida y coordinación multiagente

En la robótica industrial y de servicios, la capacidad de integrar múltiples aceleradores (GPUs, FPGAs, ASICs especializados en visión y control) y procesar datos sensoriales en milisegundos es clave para el movimiento preciso y la seguridad. PCIe 6.0 reduce la latencia en la comunicación entre sensores, unidades de procesamiento y actuadores, habilitando robots que reaccionan más rápido a cambios en su entorno y que coordinan acciones en enjambres o flotas. Esto es decisivo tanto en líneas de montaje como en robots domésticos de próxima generación.Potenciación de la Robótica doméstica e industrial

Las necesidades sociales, económicas y productivas de desarrollar la robótica, desde los cuidados a la sustitución de humanos en entornos de riesgos críticos, y desde el aumento de la capacidad de producción y logística que los robots y la automatización, mediados por la capa de inferencia, pueden aportar, hasta la robótica de precisión en cirurgía y realización de maniobras ultracomplejas de forma segura, están haciendo que uno de los entornos de crecimiento de la demanda sea precisamente los servicios y componentes clave para la fabricación y gestión de los robots.

La robótica y la robotización moderna abarca desde robots colaborativos (cobots) y vehículos autónomos hasta drones inteligentes y sistemas de domótica avanzada. Todos comparten un requisito crítico: procesar grandes flujos de datos sensoriales con latencia mínima para reaccionar en tiempo real.

- Sensores de alta densidad: Un coche autónomo genera hasta 1,2 GB/s de cámaras 8K, radar y LiDAR. Con PCIe 6.0, las ECU pueden transferir esos datos a GPUs o ASICs de inferencia sin estrangular el bus, produciendo decisiones de navegación en milisegundos.

- Robots industriales: Brazos robóticos con ciclos de control de 250 µs necesitan sincronizar múltiples servomotores y cámaras 3D. Un backplane PCIe 6.0 x8 mueve estados de posición, fuerzas y vídeo en bruto con margen de sobra, mejorando precisión y seguridad en tareas de pick-and-place.

- Dronería profesional: UAVs equipados con varios sensores (multiespectrales, térmicos) y enlaces 5G integran “mission computers” basados en SoC NVIDIA Jetson o AMD Versal. Las ranuras PCIe 6.0 habilitan módulos plug-and-play de visión por IA o radios SDR sin recableado de bus.

- Edge AI en factoría: Gateways industriales con ranuras PCIe 6.0 alojan tarjetas FPGA para inspección visual y PLC de tiempo crítico sobre TSN. Así, la línea de producción detecta defectos al vuelo y reajusta robots sin detenerse.

Empresas como NXP, Texas Instruments, NVIDIA e Intel ya muestran SoC con controladoras PCIe 6.0 integradas, apuntando a robots colaborativos más seguros y vehículos autónomos de nivel 4/5 a partir de 2026.

La otra cara de la moneda son los robots de trabajos repetitivos físicos. Como las empresas no pueden evitar competir en el mercado mundial, en la lógica de la competencia capitalista tal y como la hemos conocido, no pueden elegir sustituir trabajos humanos por trabajos robóticos en donde aquellos sean más baratos, o más competitivos. Si bien la primera líneas de sustitución de empleos está centrada ahora en la que hacen las máquinas intelectuales en forma de agentes productivos y pensadores artificiales, lo que afecta a la mayoría sino todos los trabajadores intelectuales, la robótica va a experimentar una ampliación de capacidades muy importante especialmente a medida que entra PCIe 6. En ese momento, con su momento GPT pero en la robótica que le llaman en China, alrededor de 2030, la crisis de eliminación de trabajo humano asalariado se va a agudizar también en la vertiente del trabajo manual.

Y, si bien es cierto que no solo es PCIe 6,7 y 8, sino una panoplia de impulsos de desarrollo, ampliaciones de funciones y capacidades y aumentos de medios disponibles, desde el progreso de las baterias para los robots móviles, pasando por la capacidad y el precio de los chips, y los desarrollo en manejo de la memoria y potencia de la cognición y alineamiento de la IA robótica, sin hablar de la superación de las limitaciones legales, políticas y sociales, en positivo, para realizar esos despliegues, es evidente que PCIe 6 resulta un catalizador estratégico para impulsar la gran transformación en el eje robótica.

La potenciación mutua en ciernes de la Onda Cultural post PCIe 6 y la Gran Revolución Científica General de la IA

La sexta generación de PCI Express no solo es un hito técnico: actúa como detonante sociotecnológico, impulsando lo que denomino la primera Onda cultural de la Civilización de la Inferencia. Al eliminar cuellos de botella internos a datos, procesado, criba de información, nuevas ordenaciones y reestructuraciones, arriba a una inaudita expansión social del poder de graficación y procesado de ideas e imágenes, propulsando el surgimiento de nuevas formas de crear, trabajar y relacionarnos:

La Ola Tecnológica nos esta adentrando en una Revolución Científica que ya ha empezado, como puede comprobarse con Alpha Pho y las diversas rupturas y facilitaciones en lñas matemáticas. Pero esta no es cualquier Revolución Científica, la Fase de Percusión Tecnológica está en pleno ascenso y la potencia PCIe 6, pero a la vez se están alzando dos sujetos o supersujetos colaborativos nuevos, los sujetos tecnológicos, hoy grandes llms, mañana AGIs y quizás ASIs, y los 800 millones de humanos intelectuales que son un ejército mundial intelectual de fuerza de trabajo y transformación. La convergencia colaborativa de ambas tiene un elemento cualtitativo de apoyo en PCIe 6, y 7 y 8, por nuestra parte, hemos de preparrnos exhaustivamente para hacer nuestras mejores aportaciones en esta fase histórica de la Civilización de la Inferencia o Era de la Inteligencia Artificial.

Larsoibar

Notas

(1) – Internet de las Cosas [IoT] y su volumen de datos

El Internet de las Cosas [IoT], (Internet of Things) es la red formada por miles de millones de dispositivos físicos —sensores, cámaras, electrodomésticos, vehículos, máquinas industriales, wearables, etc.— que recopilan, intercambian y procesan datos a través de Internet. Estos dispositivos integran microcontroladores y conectividad de red, lo que les permite comunicarse sin intervención humana directa.

Según previsiones de IDC, para 2025 habrá unos 41,6 mil millones de dispositivos IoT activos en el mundo. Este enorme número responde a la proliferación de sensores de bajo coste, la expansión de las redes 5G/6G, la industrialización de procesos inteligentes y la integración de IoT en sectores como la salud, la logística, la agricultura o las ciudades inteligentes.

En conjunto, estos dispositivos generarán alrededor de 79,4 zettabytes de datos anuales (1 ZB = 1021 bytes). El volumen es tan grande porque cada sensor produce datos de manera continua (lecturas de temperatura, imágenes, geolocalización, telemetría, etc.), muchas veces en alta resolución o con actualizaciones en tiempo real. A escala global, esto supone flujos de información que superan con creces los generados por el tráfico web tradicional o las redes sociales.

Fuentes: EETimes, Help Net Security, Aro.tech.

(2) – Qué es un byte, un zettabyte y cómo se miden los datos

En informática y telecomunicaciones conviven dos sistemas de prefijos: el decimal (SI), usado en discos y redes, y el binario (IEC), usado para memoria y sistemas operativos. Además, 1 byte (B) = 8 bits (b). Ojo: b es bit, B es byte.

Prefijos decimales (SI) — discos, redes, marketing

| Nombre | Símbolo | Valor | Equivalencia |

|---|---|---|---|

| Byte | B | 8 bits | — |

| Kilobyte | kB | 103 | 1.000 bytes |

| Megabyte | MB | 106 | 1.000.000 bytes |

| Gigabyte | GB | 109 | 1.000.000.000 bytes |

| Terabyte | TB | 1012 | 1.000.000.000.000 bytes |

| Petabyte | PB | 1015 | 1.000.000.000.000.000 bytes |

| Exabyte | EB | 1018 | 1.000.000.000.000.000.000 bytes |

| Zettabyte | ZB | 1021 | 1.000.000.000.000.000.000.000 bytes |

| Yottabyte | YB | 1024 | 1.000.000.000.000.000.000.000.000 bytes |

Prefijos binarios (IEC) — memoria, sistemas operativos

| Nombre | Símbolo | Valor | Equivalencia |

|---|---|---|---|

| Kibibyte | KiB | 210 | 1.024 bytes |

| Megibyte | MiB | 220 | 1.048.576 bytes |

| Gibibyte | GiB | 230 | 1.073.741.824 bytes |

| Tebibyte | TiB | 240 | 1.099.511.627.776 bytes |

| Pebibyte | PiB | 250 | 1.125.899.906.842.624 bytes |

| Exbibyte | EiB | 260 | 1.152.921.504.606.846.976 bytes |

| Zebibyte | ZiB | 270 | 1.180.591.620.717.411.303.424 bytes |

| Yobibyte | YiB | 280 | 1.208.925.819.614.629.174.706.176 bytes |

Ejemplos cotidianos

| Tipo de archivo o recurso | Tamaño típico | Equivalencia |

|---|---|---|

| Foto JPEG 12MP | 4–6 MB | ≈ 0,004–0,006 GB |

| Vídeo Full HD (1 h) | 1–3 GB | ≈ 1.000–3.000 MB |

| Vídeo 4K UHD (1 h) | 7–15 GB | ≈ 7.000–15.000 MB |

| Juego AAA moderno | 80–150 GB | ≈ 80.000–150.000 MB |

| Película Blu-ray completa | 25–50 GB | ≈ 25.000–50.000 MB |

| Base de datos empresarial grande | 5–20 TB | ≈ 5.000–20.000 GB |

| Tráfico internet mundial/día (2023) | ≈ 5 EB | ≈ 5.000.000 TB |

Resumen rápido: Un zettabyte (ZB) son 1021 bytes en decimal. En binario sería un zebibyte (ZiB) = 270 bytes. La confusión entre prefijos viene de décadas de uso indistinto; hoy la norma IEC aclara el binario.

(3) – La Latencia y su importancia

La latencia es el tiempo que tarda una señal o un dato en viajar desde su origen hasta su destino. En informática y telecomunicaciones, se mide normalmente en milisegundos (ms) o incluso en microsegundos (μs). No hay que confundirla con la velocidad de transferencia (ancho de banda): la latencia es una cuestión de “reacción”, no de “cantidad”. Un sistema puede mover muchos datos por segundo (alto ancho de banda) pero tardar demasiado en empezar a transmitirlos si la latencia es alta.

Las latencias bajas son importantes porque reducen el tiempo de respuesta en aplicaciones interactivas y de control. Esto mejora desde la fluidez en videojuegos en línea o videollamadas, hasta la coordinación de robots, vehículos autónomos o servidores que procesan inteligencia artificial en tiempo real. Cuanto menor es la latencia, más rápido puede reaccionar un sistema ante cambios, lo que se traduce en experiencias más naturales para el usuario y en una mayor seguridad y eficiencia en sistemas críticos.

(6) ¿Qué es W3C y por qué importa?

Otro consorcio de estandarización, es el célebre World Wide Web Consortium (W3C), una organización internacional sin ánimo de lucro que desarrolla estándares abiertos para la Web (HTML, CSS, accesibilidad, privacidad, etc.). Reúne a empresas miembro, equipo técnico y a la comunidad internauta para crear Recomendaciones que cualquier navegador y servicio pueda implementar, con la misión de “hacer que la Web funcione para todos”. Hoy lo lidera un Consejo y un CEO (Seth Dobbs).

El trabajo se organiza en Grupos de Trabajo (Working Groups), que redactan estándares en el “W3C Process”, y Grupos de Interés/Comunidad, que incuban ideas y uso de casos. A mediados de 2025 W3C indica decenas de Grupos de Trabajo activos.

Grupos de Trabajo clave en W3 ahora mismo y perspectivas:

| Grupo (W3C) | Foco | Próximos hitos / horizonte |

|---|---|---|

| CSS Working Group / Grupo de definición de las Hojas de Estilo en Cascada | Evolución modular de CSS (niveles, módulos, definición anual del estado de CSS). | Definiciones anuales CSS-2025/2026; continuidad de módulos (Container Queries, Color, View Transitions, etc.) |

| Web Applications WG /Grupo de Aplicaciones Web | APIs de plataforma web (manifiestos, permisos, storage, etc.). | Charter activo hasta 2026; mantenimiento/avance de APIs de apps web. |

| GPU for the Web WG /Grupo de trabajo para Gráficos Web de computación avanzada | WebGPU (gráficos y cómputo moderno en la Web) y WGSL. | Recharter vigente hasta 2026-11-30; consolidación de WebGPU en navegadores y nuevas capacidades. |

| Verifiable Credentials WG /Grupo de Trabajo para credenciales verificables | Modelo de datos y notas relacionadas para credenciales verificables. | Charter hasta 2026-10-11; mantenimiento y nuevas notas/interop. |

| Web of Things (WoT) WG /Grupo de Trabajo de estandarización del Internet de las Cosas | Estándares de IoT (Thing Description, bindings, testing). | Charter activo hasta 2025-10-02; recharter en marcha para ciclo 2025-2027. |

| Privacy WG / PING (Interest Group) / Grupo de Trabajo de Privacidad Web | Privacidad en la Web: asesoría, mitigación de huellas, nuevas propuestas. | Seguimiento transversal a otros grupos; mecanismos estándar de privacidad. |

| Internationalization WG / Grupo de Trabajo de Internacionalización | Compatibilidad de idiomas y sistemas de escritura; cierre de “gaps”. | Trabajo continuo (repositorios y pipeline de gaps |

| EPUB 3 WG /Grupo de trabajo para las especifaciones web Epub | Familia de especificaciones EPUB 3 (publicación digital). | Charter propuesto/activo para mantenimiento y mejora del ecosistema EPUB. |

Pero además, a estos grupos hay que sumar los llamados grupos experimentales que esperan en la incubadora de W3:

| Grupo de incubación (CG) | Tema / foco | WG de destino (estándar) | Estado / horizonte |

|---|---|---|---|

| WICG (Web Incubator CG) | Propuestas de plataforma web (p.ej., prioridad cargas, APIs de rendimiento, features de HTML/CSS/Storage) | Web Applications WG / HTML WG / CSS WG (según el tema) | Flujo continuo: ideas que maduran saltan a WGs; otras se archivan o iteran |

| Immersive Web CG | XR en la Web (WebXR; anchors, layers, hand-tracking) | Immersive Web WG | WebXR estabilizado; nuevos módulos en evolución |

| Web Machine Learning CG | Inferencia ML local (WebNN, modelos y backends) | Web Machine Learning WG | Especificación en curso; interoperabilidad y seguridad en foco |

| GPU for the Web CG | Gráficos y cómputo moderno (WebGPU, WGSL) | GPU for the Web WG | WebGPU consolidándose; ampliaciones/interop en seguimiento |

| WebTransport (incubación WICG) | Transporte con fiabilidad/latencia variables y múltiples flujos | WebTransport WG | APIs estabilizándose; despliegue en navegadores y CDNs |

| WebCodecs (incubación WICG) | Acceso de bajo nivel a códecs de audio/vídeo | Media WG | API usable; mantenimiento y registro de códecs |

| WebAssembly CG | Wasm (núcleo, hilos, SIMD, Component Model) | WebAssembly WG | Core maduro; Component Model en maduración |

| MiniApps CG | Aplicaciones ligeras estilo ecosistemas móviles (manifest, packaging) | MiniApps WG | Normas de interoperabilidad y empaquetado en progreso |

| OpenUI CG | Componentes UI interoperables (patrones, partes, accesibilidad) | CSS WG / WebApps WG / ARIA WG (según componente) | Patrones y acuerdos de interoperabilidad por componentes |

Nota: estos son ejemplos ilustrativos; el ecosistema W3C es dinámico. El camino típico es: CG/IG → borradores → WG → Recomendación, sujeto a pruebas, seguridad, accesibilidad e interoperabilidad.

(5) Según estimaciones de US PIRG / The Restart Project, el fin del soporte de Windows 10 podría generar 1,54 millones de toneladas métricas de residuos electrónicos. Por su parte, la consultora Canalys Research calcula que quedarían obsoletos unos 240 millones de PC, lo que equivaldría a 480 000 toneladas de material.

(4) – Tarjetas de Expansión y Placa Base

En informática, una tarjeta de expansión es un componente electrónico que se inserta en la placa base de un ordenador, mediante conector específico (generalmente PCIe), con el fin de añadir o mejorar funciones que no están integradas o que se desean potenciar. Estas funciones pueden ir desde el procesamiento de gráficos (GPU), la aceleración de inteligencia artificial (tarjetas con FPGA o ASIC), el manejo de redes (Ethernet, Wi-Fi), hasta la gestión de almacenamiento (controladoras NVMe o RAID), sonido profesional o captura de vídeo.

La placa base es el circuito principal que interconecta la CPU, la memoria y los dispositivos periféricos, y sirve de soporte físico y lógico para las tarjetas de expansión. Así, la expresión “tarjeta de expansión para la placa base” es correcta, aunque más preciso es especificar el tipo y la función, por ejemplo: “tarjeta de expansión PCIe para aceleración de IA” o “tarjeta de red PCIe de alta velocidad”.

(5) – ¿Qué es el consorcio PCI-SIG?

PCI-SIG (Peripheral Component Interconnect Special Interest Group / Grupo de Interés Especial de la Interconexión de Componentes Periféricos) es el consorcio industrial sin ánimo de lucro que define, mantiene y certifica los estándares PCI, PCI-X y, especialmente, PCI Express (PCIe). Fundado en 1992, reúne hoy a más de 1.000 empresas miembro de todo el ecosistema (fabricantes de chips y equipos, proveedores de IP y software, instrumentación de test), y coordina la evolución de la interconexión de alta velocidad que usan PCs, servidores, centros de datos y sistemas embebidos.

Además de publicar las especificaciones (por ejemplo, PCIe 6.0 en 2022 y PCIe 7.0 en 2025), PCI-SIG gestiona el programa de conformidad (talleres de pruebas y la Integrators List) para asegurar interoperabilidad y retrocompatibilidad entre generaciones. También organiza su Developers Conference anual para miembros. Gracias a este trabajo, la tecnología PCIe mantiene su ritmo histórico de duplicar el caudal por carril aproximadamente cada tres años, preservando la compatibilidad hacia atrás y la robustez del ecosistema.

Fuentes: PCI-SIG (sitio oficial) · Membership · Compliance Program · Integrators List · PCIe 7.0 (anuncio 2025) · 1.000 miembros.

(6) – La búsqueda de El Santo Grial en las AGIs y la ASI

En el campo de la inteligencia artificial, dos conceptos clave marcan el horizonte de desarrollo: la AGI (Artificial General Intelligence / Inteligencia Artificial General o IAG por sus siglas en castellano) y la ASI (Artificial Super Intelligence / Super Inteligencia Artificial, o SIA, por sus siglas en castellano).

Mientras que la IA actual está especializada en tareas concretas, la AGI aspira a igualar la versatilidad cognitiva humana y la ASI a superarla ampliamente. Estas definiciones no solo son técnicas, sino que implican profundas consecuencias para la economía, la ciencia, la ética, la ciencia, la filosofía y la sociedad en general.

- AGI (Artificial General Intelligence): inteligencia artificial con capacidad de aprendizaje, razonamiento y adaptación a una amplia gama de tareas y contextos, comparable a la inteligencia humana. Puede transferir e interrelacionar conocimientos de un dominio a otro, o entre muchos multilateralmente, resolver problemas nuevos y comprender conceptos abstractos. La AGI no existe todavía, pero su desarrollo es uno de los grandes objetivos —y retos— de la investigación en IA.

- ASI (Artificial Superintelligence): forma hipotética de inteligencia artificial que supera la capacidad cognitiva de los mejores cerebros humanos en prácticamente todos los campos, incluidos la creatividad científica, la resolución de problemas complejos y las habilidades sociales. Una ASI podría mejorar y rediseñar sus propios sistemas, generando un crecimiento intelectual exponencial. Su eventual aparición plantea retos de control y gobernanza global sin precedentes.

La distinción entre AGI y ASI es esencial para el debate sobre el futuro de la tecnología y su impacto en la humanidad. Mientras la AGI representaría un punto de inflexión en nuestra relación con las máquinas, la ASI implicaría un cambio de paradigma potencialmente irreversible en la civilización, con implicaciones tanto prometedoras como riesgosas.

(7) – ¿Por qué PCIe 6.0 ayuda a acelerar el entrenamiento de modelos de IA?

En el entrenamiento distribuido de modelos de inteligencia artificial, varias GPUs trabajan en paralelo, cada una con una copia del modelo. Tras procesar sus datos, calculan los gradientes (las correcciones necesarias para mejorar el modelo) y deben sincronizarlos con las demás GPUs antes de actualizar los pesos. Esta fase de intercambio se llama all-reduce y consume tiempo en cada ciclo de entrenamiento.

Cuanto mayor es el ancho de banda de la interconexión entre GPUs, menor es el tiempo de sincronización, y más rápido se completa cada ciclo de entrenamiento.

Ejemplo simplificado: Imaginemos un modelo de 1.000 millones de parámetros en formato FP16 (2 bytes por parámetro), lo que genera gradientes de unos 2 GB por GPU. Si entrenamos con 8 GPUs y usamos PCIe 5.0 (64 GB/s teóricos, ~50 GB/s efectivos), el intercambio completo de gradientes podría tardar unos 0,08 segundos por ciclo. Al pasar a PCIe 6.0 (128 GB/s teóricos, ~100 GB/s efectivos), el mismo intercambio bajaría a 0,04 segundos.

Si el ciclo total de entrenamiento (cálculo + sincronización) duraba 0,28 s, ahora duraría 0,24 s. Puede parecer poco, pero en millones de ciclos, la diferencia implica días o incluso semanas menos de entrenamiento para el mismo modelo.

(8) – Silicio Inteligente

Cuando la generación PCIe 5.0 esté consolidada en el mercado de consumo yel parque mundial de ordenadores (ver anexos), el crecimiento de PCIe 6.0, llegado a determinado punto, permitirá integrar arquitecturas heterogéneas en las que chips especializados (GPU, TPU, FPGA, ASIC y otros tipos de “silicio inteligente”) estén tan presentes como la memoria DRAM en cualquier ordenador. Esto significa que, gracias al aumento drástico de ancho de banda y reducción de latencia, estos procesadores especializados podrán conectarse y trabajar junto a la CPU con cuellos de botella mínimos, haciendo que la computación heterogénea sea la norma y no la excepción.

En la práctica, implicará que dispositivos desde portátiles, pasando por PCs y workstations hasta servidores y sistemas embebidos podrán incluir múltiples aceleradores adaptados a tareas concretas (visión artificial, IA conversacional, modelado 3D, simulación física, etc.), comunicándose a velocidades cercanas a la memoria principal y mejorando radicalmente la capacidad de cómputo por vatio.Cuando nos referimos a “sistemas embebidos” en este contexto, el término abarca cualquier dispositivo que integra un ordenador para funciones específicas, sin ser un PC de propósito general. Esto incluye smartphones y tablets, placas ARM de bajo consumo como Raspberry Pi, Orange Pi o Jetson Nano, así como controladores industriales, dispositivos IoT avanzados, sistemas electrónicos en automoción y equipamiento médico. En muchos de estos casos, el estándar PCIe 6.0 no se presenta como un slot físico, sino como un bus interno de alta velocidad que conecta aceleradores, módulos de comunicaciones o procesadores gráficos directamente dentro del sistema, adoptando la misma filosofía de integración que en equipos de escritorio y servidores.

(9) Infografía: Ecosistema PCIe — impacto 2025 → 2040 (síntesis)

Impacto directo (2025)

≈ 190 mil millones USD en ventas de hardware que depende directamente de PCIe (GPUs, SSD NVMe, placas base, servidores, NIC, etc.).

Equivale a ~0,18 % del PIB mundial.

Impacto indirecto inmediato (2025)

Servicios habilitados por infraestructura PCIe (nube, IA, redes sociales, videojuegos, contenidos, PYMEs): ~1,1–1,3 billones USD.

> 1 % del PIB mundial.

Proyección 2040

Sectores habilitados por PCIe podrían mover alrededor de ~9 billones USD/año (≈ 8 % del PIB mundial).

Tracción: nube, IA/HPC, almacenamiento NVMe, redes 800 GbE→1.6 TbE, CXL sobre PCIe 6/7.

| Bloque habilitado por PCIe | 2025 (USD) | 2040 (USD) |

|---|---|---|

| Computación en la nube | ~912 mil millones | ~7,4 billones |

| IA / Data Centers | ~300 mil millones | ~1,25 billones |

| Videojuegos y contenidos | ~189 mil millones | ~350 mil millones |

| Total estimado | ~1,4 billones | ~9 billones |

(10) Importancia de PCIe 6 y CXL parael desarrollo de la intelectrónica doméstica

Idea clave: PCIe 6 (64 GT/s) y CXL (Compute Express Link) forman el tándem que permite memoria elástica y aceleración en equipos locales. PCIe 6 aporta el transporte de muy alto ancho de banda; CXL añade coherencia y tiering de memoria entre CPU, GPU y dispositivos. Juntos abren la puerta a nodos “edge” domésticos capaces de servir experiencias XR/holográficas e IA personal y de gestión robótica sin depender tanto de la nube de ordenadores corporativos y allí donde llegan.

Estado actual (2025): CXL está enfocado a centros de datos y algunas workstations. En consumo, faltan plataformas con CXL habilitado (CPU/chipset/placas), firmware UEFI/ACPI con CEDT, y un soporte maduro en sistemas de escritorio (Windows, Linux, Harmony o Mac cliente). Además, los expansores de memoria y switches CXL siguen siendo caros y con requisitos térmicos propios del datacenter.

Por qué importa para el hogar “avanzado”: la intelectrónica doméstica—IA local, robots/asistentes, metaverso productivo, holografía/XR—demanda ráfagas de RAM y VRAM muy superiores a las de un PC estándar. PCIe 6 crea canales rápidos para SSD NVMe, NIC de 800 GbE→1.6 TbE y GPUs modernas; CXL permite sumar cientos de GB o TB como memoria ampliada con coherencia razonable, útil para modelos multimodales, render volumétrico o bases de datos in-memory.

- Beneficio práctico: subir de 128–256 GB DRAM a 1–4 TB “efectivos” con CXL (a mayor latencia que la DRAM, pero suficiente para IA local y edición 3D pesada).

- Arquitectura doméstica: mini-servidor (edge node) con CPU+GPU/NPU, PCIe 6 amplio y ranuras libres; cliente XR/holográfico de baja latencia; red 10 GbE/25 GbE; NVMe Gen5/Gen6.

- Limitaciones: más latencia que DRAM, consumo y ruido mayores, y competencia por líneas PCIe con GPU/almacenamiento.

| Periodo | Expectativa | Casos de uso |

|---|---|---|

| 2025–2027 | Nicho (DC/HPC; pocas workstations) | IA/analítica grande, laboratorio |

| 2028–2031 | Prosumer inicial (sobre PCIe 6) | IA local pesada, XR avanzada, render volumétrico |

| 2032–2035 | Workstations “creator/AI” y pymes técnicas | Tiering DRAM+CXL, EDA/visualización compleja |

| 2036–2040 | Más común en nodos edge domésticos | Memoria compartida (CXL 3.x), hot-plug, flujos XR/IA continuos |

Recomendación hoy: preparar el equipo para el salto (placas con muchas líneas PCIe, chasis y PSU holgados, NVMe Gen5/6, 10 GbE) y mantener Linux/KVM al día en el nodo “edge”. Incorporar CXL cuando lleguen placas “creator/WS” con soporte estable y el coste/GB sea razonable.

Glosario: BD in-memory = bases de datos que operan principalmente en RAM (p. ej., SAP HANA, Redis); EDA = Electronic Design Automation (herramientas para diseñar chips, muy intensivas en memoria/cómputo).

(11) Cronograma de la Sub-Ola Tecnológica PCIe 6 (y previsiones de PCIe 7 y pcie 8)

Todo lleva a pensar que, salvo cisnes negros, el despliegue de PCIe 6 seguirá un ritmo escalonado, empezando por centros de datos y hardware especializado antes de llegar al mercado de consumo y luego a masificarse. El PCI-SIG mantiene su cadencia de «duplicar el ancho de banda cada 3 años», por lo que la ventana 2024-2030 será crucial para la consolidación de la sexta generación y el aterrizaje preliminar de PCIe 7.

| Año | Hito PCIe 6.0 | Difusión estimada | Hito PCIe 7.0 | Difusión estimada |

|---|---|---|---|---|

| 2022 | Especificación 1.0 final Inicio de IP/PHY en laboratorios | Validación de silicio y pruebas SI | — | — |

| 2024 | Demostraciones públicas (FMS, DesignCon) Retimers y switches prototipo | Equipos de test, Early-Access cards | Borrador 0.7 publicado | Revisión de miembros |

| 2025 | Lista de Integradores PCIe 6 Primeros servidores IA Q4 | Centros de datos hiperescala/HPC | Especificación 1.0 (junio) | Path-finding óptico y cables activos |

| 2026 – 2027 | Workstations profesionales, edge servers | Empresa y telecom | Primeros test-chips Gen 7 | Alpha silicon |

| 2028 – 2029 | Placas base entusiastas, SSD Gen 6 | Consumo avanzado / prosumers | Plataformas HPC piloto | Centros de datos selectos |

| 2030+ | Masificación en PC de gama media | Mercado mainstream | Servidores generalistas Gen 7 | Despliegue amplio 2030-2031 |

Nota: Las fechas son orientativas, basadas en declaraciones de fabricantes (Broadcom, Intel, AMD) y en la propia hoja de ruta del PCI-SIG. La adopción en el ecosistema de consumo suele retrasarse 2-3 años respecto al segmento servidor.

Esto lo escribo en el tercer trimestre de 2025, y si todo esto es correcto, tenemos que entender que hacia 2030 también la Robotización y la robótica urbana van a ser cotidianas en el día a día. Unos cuatro años. ¿Qué impacto cultural, ideológico, político, ideológico, a partir de los nuevos usos y costumbres y la adaptación relativa de los actuales, va a tener la sub-ola PCIE.6?

Cronograma de microprocesadores 2025 – 2030 (RISC-V, ARM y x86)

Las fechas son estimaciones basadas en roadmaps públicos de fabricantes (Intel, AMD, Apple, Qualcomm, NVIDIA, SiFive, Samsung Foundry, TSMC) y anuncios de fundición. Pueden variar según avances de litografía y demanda de mercado.

| Año | Arquitectura / Producto clave | Empresa | Nodo (nm) | Comentarios |

|---|---|---|---|---|

| 2025 | Intel Arrow Lake (x86) | Intel | Intel 20A | Primer uso comercial de RibbonFET y PowerVia; orientado a escritorio enthusiast |

| 2025 | Zen 5 c. “Granite Ridge” (x86) | AMD | TSMC N3E (3 nm) | Arquitectura modulable; CCD de 3 nm + IOD de 6 nm; PCIe 6 en servidores EPYC “Turin” |

| 2025 | Apple M4 (ARMv9) | Apple Silicon | TSMC N3B | MacBook Pro/Ultra; motor IA mejorado y GPU ray-tracing de 8 nm EUV interno |

| 2026 | Qualcomm Oryon X2 (ARMv9) | Qualcomm | TSMC N3P | CPU para portátiles Windows-on-ARM; memoria LPDDR6 + PCIe 6.0 |

| 2026 | NVIDIA Grace Next (ARM Neoverse) | NVIDIA | TSMC N3X | Enlace NVLink 4 + PCIe 6 para clústeres IA exascala |

| 2027 | Intel Panther Lake (x86) | Intel | Intel 18A | Nodo con High-NA EUV; cache 3D-Foveros; módulos CXL 3.0 |

| 2027 | AMD Zen 6 “Morocco” (x86) | AMD | TSMC N2 | CCD en 2 nm, IOD 4 nm; primera generación x86 bajo 2 nm |

| 2027 | RISC-V – SiFive Performance P700 | SiFive / Samsung Foundry | Samsung SF3E (3 nm GAA) | CPU de alto rendimiento para servidores edge; compatibilidad PCIe 6 |

| 2028 | Apple M5 (ARMv9) | Apple Silicon | TSMC N2P (2 nm) | Arquitectura chiplet con DRAM on-package (InFO-SoW) |

| 2028 | Qualcomm Snapdragon X5 (ARM) | Qualcomm | TSMC N2 | SoC para XR y AI edge; motor NPU > 100 TOPS |

| 2029 | Intel Nova Lake (x86) | Intel | Intel 14A | Probable integración fotónica; PCIe 7 adoptado |

| 2029 | NVIDIA Grace Ultra (ARM) | NVIDIA | TSMC A14 (1.4 nm est.) | CPU-GPU coherente para IA generativa a escala zettaFLOP |

| 2030 | AMD Zen 7 (x86) | AMD | TSMC A14 | Chiplets 3D empacados con memoria HBM4E; interfaz PCIe 7 & CXL 4 |

| 2030 | RISC-V – OpenTitan Next | Google / Community | GlobalFoundries 12FDX+ (12 nm FD-SOI) | Nodo maduro optimizado para seguridad embebida y consumo ultrabajo |

Nota: Los nodos N3E/N3P/N3X corresponden a variantes optimizadas del proceso 3 nm de TSMC; 20A/18A/14A son la nomenclatura de Intel “Ångström” nodes. Fechas posteriores a 2028 pueden sufrir variaciones según la disponibilidad de High-NA EUV y la capacidad de las fundiciones.

2) Historia resumida de los estándares PCI Express 1.0 → 6.0 (2003 – 2025)

Desde 2003 cada generación de PCI Express (PCIe) ha duplicado el ancho de banda, impulsando la adopción de GPUs cada vez más potentes, SSD NVMe ultra-rápidos y redes internas de servidor. A continuación se muestra la cronología de lanzamiento y masificación estimada.

| Año especificación | Generación / Velocidad | Sistemas instalados* (≈) | Periféricos emblemáticos | Impacto clave |

|---|---|---|---|---|

| 2003 | PCIe 1.0 — 2.5 GT/s (~4 GB/s x16) | ≈ 120 M PCs (2003-2007) | GPU NVIDIA GeForce 6800, sound cards X-Fi | Sustituye al bus PCI y AGP; primer salto a serie full-dúplex. |

| 2007 | PCIe 2.0 — 5 GT/s (~8 GB/s x16) | ≈ 350 M PCs (2007-2012) | AMD Radeon HD 4870, primeras controladoras SATA 6 Gb/s | Permite GPUs dual slot de 150 W y tarjetas RAID de 8 puertos. |

| 2010 | PCIe 3.0 — 8 GT/s (~16 GB/s x16) | ≈ 600 M PCs/Workstations + 3 M servidores (2012-2018) | SSD NVMe Gen3, GPU GTX 1080, redes 40 GbE | Primera oleada de SSD PCIe > 2 GB/s, GPUs 4K y HBM1. |

| 2017 | PCIe 4.0 — 16 GT/s (~32 GB/s x16) | ≈ 90 M sistemas (2019-2023) (desktop Ryzen 3000, PS5 / Xbox SX) | SSD Gen4 7 GB/s, GPU RDNA2, NIC 100 GbE | Revoluciona tiempos de carga en consolas y HPC GPU clusters. |

| 2019 | PCIe 5.0 — 32 GT/s (~64 GB/s x16) | ≈ 10 M servidores (2022-2024) ≈ 15 M desktops entusiasta | GPU NVIDIA H100, SSD Gen5 14 GB/s, NIC 400 GbE | Alimenta IA training clusters y tarjetas OCP 3.0 400 GbE. |

| 2022 | PCIe 6.0 — 64 GT/s (~128 GB/s x16) | Adopción inicial en 2025: ≈ 100 k servers AI/HPC | GPU Blackwell B200, SSD Gen6 30 GB/s, CXL 3.0 switches | PAM4 + FEC; desbloquea pools de memoria coherente y redes 800 GbE. |

3) Impacto acelerador por categoría de componente

- Tarjetas gráficas – Cada salto de ancho de banda ha permitido buses de textura más anchos, soporte multi-GPU (SLI/CrossFire, NVLink) y mayor consumo: de 75 W en PCIe 1.0 a 450 W en Gen5 x16 con conectores 16-pin 12VHPWR.

- Almacenamiento SSD – Pasamos de SATA 3 Gb/s (≈300 MB/s) a NVMe Gen6 cercano a 30 GB/s, haciendo factible el direct-storage y bases de datos in-memory.

- Redes y puertos – NICs 10 GbE → 400 GbE (Gen5) y 800 GbE (Gen6); expansión de puertos USB-4, Thunderbolt 5 y tarjetas capture 8K.

- Memoria y CPU – Curva de consumo DDR2 → DDR5; CXL 3.0 sobre PCIe 6 habilita “memory pooling” entre CPU y GPU, reduciendo copias y latencia.

- Fuentes de alimentación – El límite de slot 75 W permanece, pero conectores auxiliares pasan de 6-pin (75 W) a 16-pin (600 W) para GPUs Gen5/Gen6.

En conjunto, la evolución de PCIe ha sido el acelerador silencioso tras cada ola de rendimiento en PC, consola y servidor: aumentó 32× el ancho de banda en dos décadas, posibilitando la revolución gráfica 4K-8K, la explosión de la IA y el auge de los SSD NVMe.

4) Distribución estimada de los estándares PCI Express en el parque mundial (agosto 2025)

La siguiente estimación combina envíos históricos (IDC, Gartner, Canalys) y ciclos medios de renovación (≈ 5 años en PC; 4-5 años en servidor) para ofrecer una foto de cuántos equipos usan cada generación PCIe a mediados de 2025.

Parque global de PC (≈ 1,6 miles de millones de unidades)

| Generación PCIe | Cuota estimada 2025 | Observaciones |

|---|---|---|

| PCIe 1.0 / 2.0 | ≈ 18 % | Equipos corporativos legacy; HDD o SSD SATA |

| PCIe 3.0 | ≈ 50 % | Intel Haswell → Comet Lake, AMD Bulldozer → Zen 1 |

| PCIe 4.0 | ≈ 22 % | Ryzen 3000/5000, Intel Rocket/Alder Lake; SSD Gen4 |

| PCIe 5.0 | ≈ 8 % | Plataformas AM5 y Z690/Z790 entusiasta; SSD Gen5 |

| PCIe 6.0 | < 1 % | Solo placas de prueba; sin presencia retail |

Parque global de servidores (≈ 75 millones de nodos)

| Generación PCIe | Cuota estimada 2025 | Escenario típico |

|---|---|---|

| PCIe 2.0 | ≈ 4 % | Racks legacy con GPUs Kepler, NIC 10 GbE |

| PCIe 3.0 | ≈ 40 % | Xeon E5 v3/v4, EPYC Rome; NIC 25-40 GbE |

| PCIe 4.0 | ≈ 35 % | EPYC Milan, Xeon Ice Lake; SSD Gen4, NIC 100 GbE |

| PCIe 5.0 | ≈ 20 % | EPYC Genoa, Xeon Emerald Rapids; GPU A100/H100 |

| PCIe 6.0 | < 1 % | Pilotos IA/HPC con CXL 3.0 y switches Broadcom Gen6 |

Nota: porcentajes orientativos; no existen auditorías públicas que desglosen la generación PCIe exacta de cada equipo. Representan órdenes de magnitud basados en envíos acumulados y tasas de reemplazo.

5) Proyección de distribución de estándares PCI Express (2030 y 2035)

Hipótesis principales: cadencia PCI-SIG de duplicar rendimiento cada 3 años; ritmo de sustitución ~20 % del parque PC por año y ~25 % del parque servidor; llegada de PCIe 7 al «early mainstream» servidor en 2029 y al consumo entusiasta en 2032.

Parque mundial de PC (≈ 1,5 – 1,6 miles de millones de unidades)

| Estándar | Cuota estimada 2030 | Cuota estimada 2035 | Comentarios clave |

|---|---|---|---|

| PCIe 1.0 / 2.0 | ≈ 3 % | ≈ 1 % | PC corporativo legacy en mercados emergentes |

| PCIe 3.0 | ≈ 25 % | ≈ 5 % | Desktops y portátiles 2012-2018 que siguen operativos |

| PCIe 4.0 | ≈ 35 % | ≈ 20 % | Ryzen 3000/5000, Intel Rocket/ Alder Lake mainstream |

| PCIe 5.0 | ≈ 25 % | ≈ 30 % | Plataformas AM5, LGA 1700/1851 y consolas Gen11 |

| PCIe 6.0 | ≈ 10 % | ≈ 35 % | Primeros chipsets consumo 2027-2028; SSD Gen6 y GPU Gen6 |

| PCIe 7.0 | < 1 % | ≈ 10 % | Llega a entusiastas en 2032-2033 (nodo < 1 nm) |

Parque mundial de servidores (≈ 80 millones de nodos en 2030)

| Estándar | Cuota estimada 2030 | Cuota estimada 2035 | Comentarios clave |

|---|---|---|---|

| PCIe 3.0 | ≈ 8 % | ≈ 1 % | Racks legacy sin GPU moderna |

| PCIe 4.0 | ≈ 15 % | ≈ 4 % | EPYC Milan / Xeon Ice Lake que siguen amortizándose |

| PCIe 5.0 | ≈ 45 % | ≈ 20 % | Plataformas Genoa, Emerald Rapids, Graviton 5 |

| PCIe 6.0 | ≈ 30 % | ≈ 45 % | Racks IA/HPC con CXL 3.0 y NIC 800 GbE |

| PCIe 7.0 | ≈ 2 % | ≈ 30 % | Centros de datos exascala; despliegue masivo 2032-2034 |

Lectura rápida: en 2030 la mayoría de PC seguirá repartida entre PCIe 3/4/5, con la 6ª generación aún en ascenso. En servidores, PCIe 5 dominará, pero la 6 ª generación llegará a

Glosario de Acrónimos

- AGI

- ADAS: Advanced Driver Assistance Systems / Sistemas avanzados de asistencia al conductor

- AR: Augmented Reality / Realidad aumentada

- ASI

- ASIC: Application‑Specific Integrated Circuit / Circuito integrado de aplicación específica

- BCI: Brain‑Computer Interface / Interfaz cerebro‑computadora

- CPU: Central Processing Unit / Unidad central de procesamiento

- CXL: Compute Express Link / Enlace exprés de cómputo

- ECU: Electronic Control Unit / Unidad de control electrónico

- FEC: Forward Error Correction / Corrección de errores hacia adelante

- FLIT: Flow Control Unit / Unidad de control de flujo

- FPGA: Field‑Programmable Gate Array / Matriz de compuertas programable en campo

- GPU: Graphics Processing Unit / Unidad de procesamiento gráfico

- GT/s: GigaTransfers per second / Gigatransferencias por segundo

- IA: Inteligencia Artificial / Artificial Intelligence

- IoT: Internet of Things / Internet de las cosas

- LiDAR: Light Detection and Ranging / Detección y localización por luz

- NRZ: Non‑Return‑to‑Zero / No retorno a cero

- NVMe: Non‑Volatile Memory Express / Memoria no volátil exprés

- PAM4: Pulse Amplitude Modulation 4‑level / Modulación de amplitud de pulso de 4 niveles